# **DI-51** Design Idea **DPA-Switch**®

## 5 W Flyback DC-DC Converter

| Application     | Device  | Power Output | Input Voltage | Output Voltage | Topology |

|-----------------|---------|--------------|---------------|----------------|----------|

| DC-DC Converter | DPA423R | 5 W          | 36 – 75 VDC   | 5 V            | Flyback  |

#### **Design Highlights**

- Small footprint: 35 mm x 20 mm (1.4 in. x 0.8 in.)

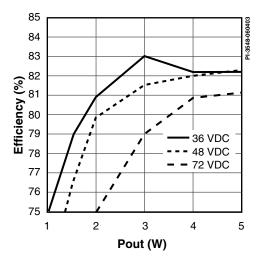

- High efficiency flyback (>80% min.)

- 8.8 W per cu. in.

- · Low component count

- Accurate line OV and UV protection

- Thermal, short circuit and output overload protection

- No current sense components

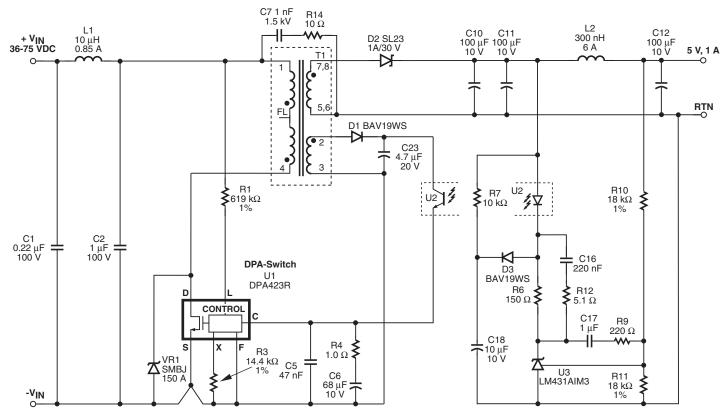

#### **Operation**

DPA-Switch greatly simplifies the design compared to a discrete implementation. Resistor R1 sets the input under/over voltages to 33 V and 86 V, respectively. Including tolerances, these thresholds guarantee the converter is operational between 36 V and 75 V without the cost of additional line sense components. Resistor R3

programs the internal current limit of the DPA423R to 53% of nominal. This limits the overload power that can be delivered in a fault condition.

Zener VR1 clamps the leakage inductance spikes to keep the DRAIN voltage at a safe level. The bias supply for U1 is provided from the auxiliary flyback transformer winding (pins 2 and 4), rectified and filtered by diode D1 and capacitor C23.

A snubber for diode D2 (capacitor and resistor) can be used, but was not needed in this application. Inductor L2 and capacitor C12 form a post filter to reduce high frequency output switching ripple. A soft-finish network, C18, D3 and R7, eliminates output turn-on overshoot. The remaining components provide output voltage regulation and loop compensation.

Figure 1. DPA-Switch Flyback DC-DC Converter.

PI-3547-062403

www.powerint.com July 2003

### **Key Design Points**

- For the nominal under-voltage set point V\_IIV.

- R1 =  $(V_{UV} 2.35) / 50 \mu A$  $V_{OV} = (R1 \times 135 \mu A) + 2.5 V$

- For highest efficiency designs: use continuous conduction mode operation designed at approximately 0.4 K<sub>RP</sub>; minimize turns in the transformer while keeping AC flux density (BM) <3000 Gauss; fully fill a single layer for each winding to minimize leakage inductance and maximize copper fill factor; use a Schottky rectifying diode (D2) with a low forward drop (in this case, the SL23 diode has a V<sub>s</sub> = 0.320 V at 125 °C/2A).

- Resistor R3: the PIXIs spreadsheet calculates the peak current (IP) of the power supply. Resistor R3 is chosen to set the

Figure 2. Efficiency vs. Output Power.

- internal current limit 10% to 15% above the calculated IP value. This limits overload power (worst case is at high input line).

- Set resonant frequency of post-filter (L2, C12) beyond crossover frequency (typically 5% to 10% of switching frequency).

- For main secondary current loop from transformer pin 8 to diode D2 and capacitors C10, C11 and back to pin 6 of the transformer: ensure identical path length for C10 and C11 to guarantee they equally share the ripple current.

- Due to the very tight size constraints on this power supply, the drain voltage traces should be kept as short as possible and where possible, shielded by surrounding them with source potential traces. This will prevent noise coupling to the lowvoltage signal pins of the DPA-Switch.

| Transformer Parameters         |                                                                                        |  |  |

|--------------------------------|----------------------------------------------------------------------------------------|--|--|

| Core Material                  | EFD-10 Ferroxcube 3F3, AL of 100 nH/T <sup>2</sup>                                     |  |  |

| Bobbin                         | EDF-10 8 pin (or equivalent)                                                           |  |  |

| Winding Order<br>(pin numbers) | 1/2 Primary: (1–FL), tape<br>Bias: (4–3), 5 V (5–8), tape<br>1/2 Primary: (FL–2), tape |  |  |

| Primary Inductance             | 174 μH, ±10%                                                                           |  |  |

| Primary Resonant<br>Frequency  | 4.7 MHz (minimum)                                                                      |  |  |

| Leakage<br>Inductance          | 1.0 μH (maximum)                                                                       |  |  |

Table 1. Transformer Parameters.

Power Integrations 5245 Hellyer Avenue San Jose, CA 95138, USA. Main: +1 408-414-9200 Customer Service Phone: +1-408-414-9665 Fax: +1-408-414-9765 Email: usasales@powerint.com

On the Web www.powerint.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS. The products and applications illustrated herein (transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations' patents may be found at www.powerint.com. Power Integrations grants its customers a license under certain patent rights as set forth at http://www.powerint.com/ip.htm.

The PI logo, TOPSwitch, TinySwitch, LinkSwitch, DPA-Switch, PeakSwitch, EcoSmart, Clampless, E-Shield, Filterfuse, StackFET, PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2003, Power Integrations, Inc.